# Single-Supply, Auto-Zero Sensor Amplifier with Programmable Gain and Offset

#### FEATURES

www.ti.com

- Digital Calibration for Bridge Sensors

- Offset Select: Coarse and Fine

- Gain Select: Coarse and Fine

- Bridge Fault Monitor

- Input Mux for Lead Swap

- Over/Under Scale Limits

- D<sub>OUT</sub>/ V<sub>OUT</sub> Clamp Function

- Seven Banks OTP Memory

- One-Wire Digital UART Interface

- Operating Voltage: +2.7V to +5.5V

- Temperature Range: -40°C to +125°C

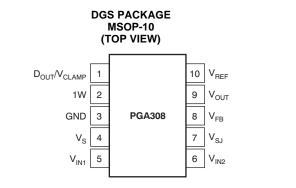

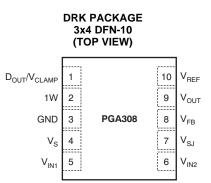

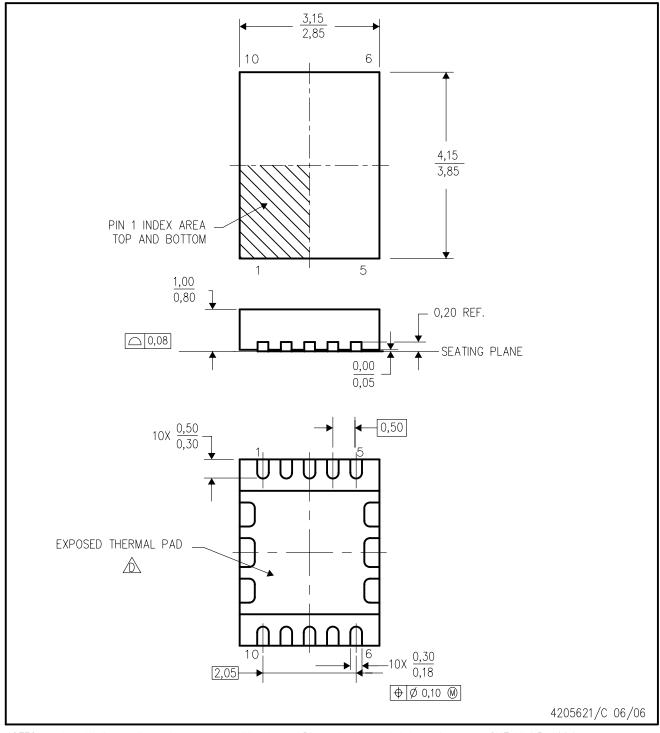

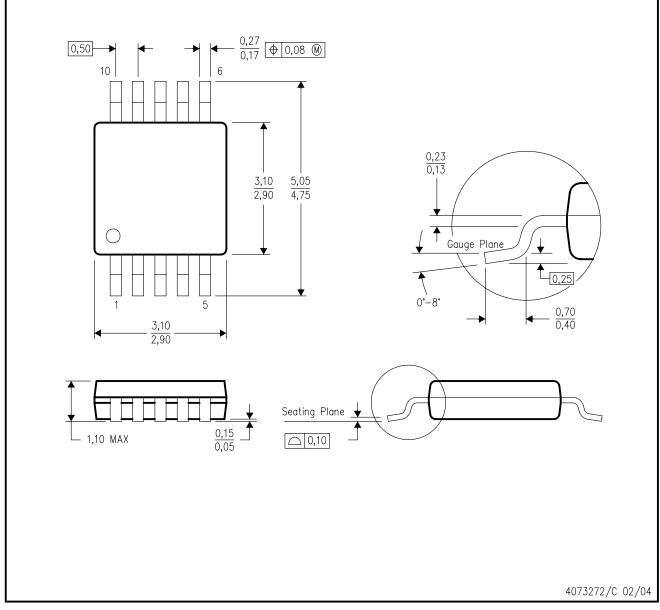

- MSOP-10 and 3mm x 4mm DFN-10 Packages

#### **APPLICATIONS**

- Bridge Sensors

- Remote 4-20mA Transmitters

- Strain, Load, Weigh Scales

- Automotive Sensors

#### **EVALUATION TOOLS**

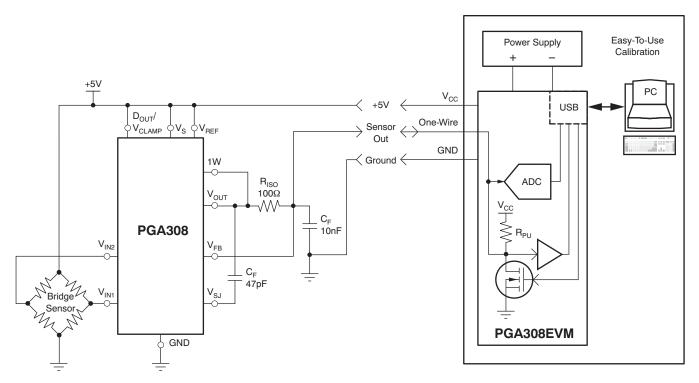

- PGA308EVM (Hardware and Software)

- Calibration and Configuration

- Sensor Emulation

#### DESCRIPTION

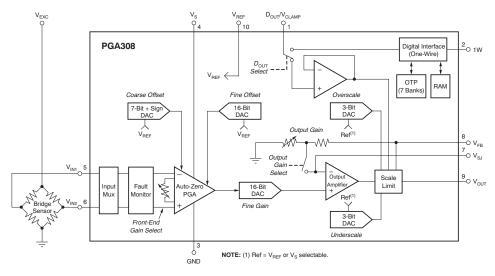

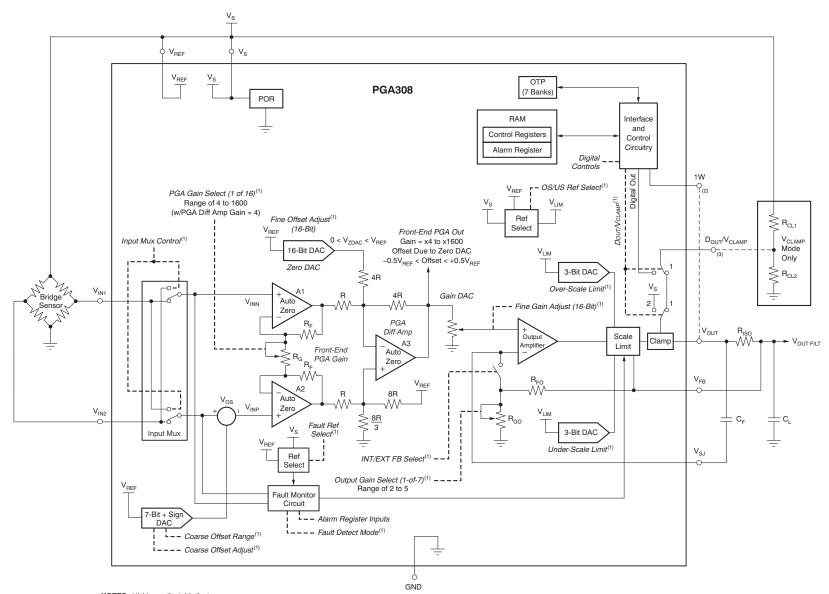

The PGA308 is a programmable analog sensor signal conditioner. The analog signal path amplifies the sensor signal and provides digital calibration for offset and gain. Calibration is done via the 1W pin, a digital One-Wire, UART-compatible interface. For three-terminal sensor modules, 1W may be connected to  $V_{\mbox{\scriptsize OUT}}$  and the assembly programmed through the V<sub>OUT</sub> pin. Gain and offset calibration parameters are stored onboard in seven banks of one-time programmable (OTP) memory. The power-on reset (POR) OTP bank may be programmed a total of four times.

The all-analog signal path contains a 2x2 input multiplexer (mux) to allow electronic sensor lead swapping, a coarse offset adjust, an auto-zero programmable gain instrumentation amplifier (PGA), a fine gain adjust, a fine offset adjust, and a programmable gain output amplifier. Fault monitor circuitry detects and signals sensor burnout, overload, and system fault conditions. Over/under-scale limits provide additional means for system level diagnostics. The dual-use D<sub>OUT</sub>/V<sub>CLAMP</sub> pin can be used as a programmable digital output or as a V<sub>OUT</sub> over-voltage clamp.

For detailed application information, see the PGA308 User's Guide (SBOU069) available for download at www.ti.com.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

| PRODUCT | PACKAGE-LEAD                    | PACKAGE<br>DESIGNATOR | PACKAGE<br>MARKING |

|---------|---------------------------------|-----------------------|--------------------|

| PGA308  | MSOP-10                         | DGS                   | P30A               |

| FGA300  | 3mm x 4mm DFN-10 <sup>(2)</sup> | DRK                   | P30B               |

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Available Q1, 2009.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

|                                         | PARAMETER                                                                                                      | PGA308                            | UNIT |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------|------|

| Supply Voltage,                         | V <sub>S</sub>                                                                                                 | +5.5                              | V    |

| D <sub>OUT</sub> /V <sub>CLAMP</sub> Ou | tput Current Limit                                                                                             | ±10                               | mA   |

|                                         | Input Current                                                                                                  | -10 to +10                        | mA   |

|                                         | $V_{\text{IN1}}, V_{\text{IN2}}, V_{\text{REF}}, 1W, D_{\text{OUT}} / V_{\text{CLAMP}}, V_{\text{SJ}}{}^{(2)}$ | GND – 0.3 to V <sub>S</sub> + 0.3 | V    |

| Pin Protection                          | V <sub>FB</sub> Terminal Voltage                                                                               | -30 to 30                         | V    |

|                                         | V <sub>FB</sub> Terminal Current                                                                               | -10 to 10                         | mA   |

|                                         | V <sub>OUT</sub>                                                                                               | -160 to 160                       | mA   |

| Operating Tempe                         | erature Range                                                                                                  | -40 to +150                       | °C   |

| Storage Temperature Range               |                                                                                                                | -55 to +150                       | °C   |

| Junction Temperature                    |                                                                                                                | +165                              | °C   |

| ESD Ratings                             | Human Body Model (HBM)                                                                                         | 2000                              | V    |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

(2) Terminals are diode-clamped to the power-supply rails, V<sub>S</sub> and GND. Limit current to 10mA or less.

#### ELECTRICAL CHARACTERISTICS

Boldface limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to +125°C.

At  $T_A = +25^{\circ}$ C,  $V_S = +5V$ , GND = 0V,  $D_{OUT}/V_{CLAMP} = +5V$ , and  $V_{REF} = +5V$ , unless otherwise noted.

|                                                                                                                 |                                                                                                                                                                                                       |      | _                      |                          |               |  |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|--------------------------|---------------|--|

| PARAMETER                                                                                                       | CONDITIONS                                                                                                                                                                                            | MIN  | TYP                    | MAX                      | UNIT          |  |

| V <sub>ouπ</sub> /V <sub>N</sub> Differential Signal Gains <sup>(1)</sup><br>(Front-End PGA + Output Amplifier) | Front-End PGA gains (G <sub>F</sub> ): 4, 6, 8, 12, 16, 32, 64, 100, 200,<br>400, 480, 600, 800, 960, 1200, 1600<br>Output Amplifier gains: 2, 2.4, 3, 3.6, 4, 4.5, 6<br>Fine Gain Adjust = 0.33 to 1 | 2.67 |                        | 9600                     | V/V           |  |

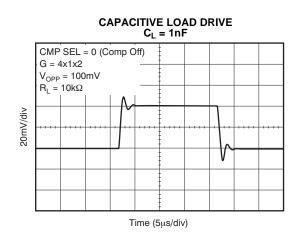

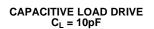

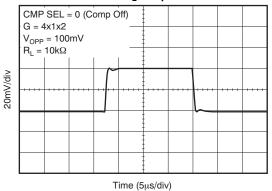

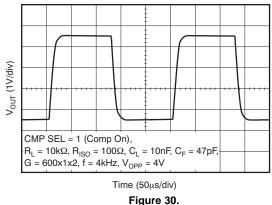

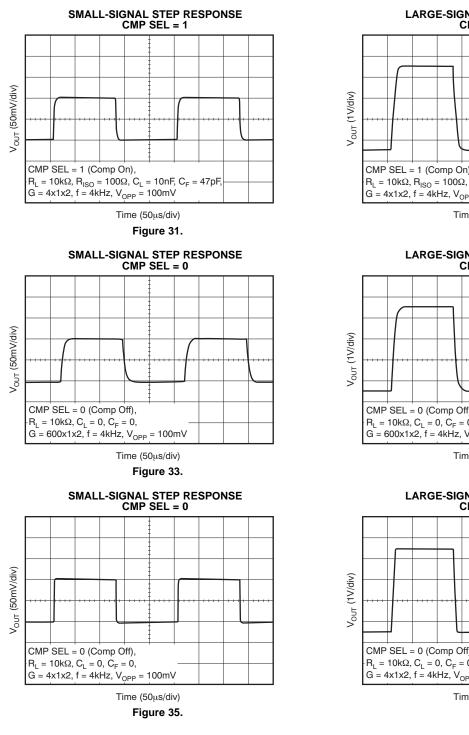

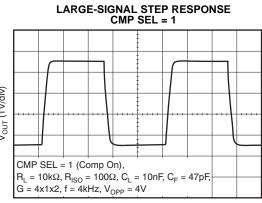

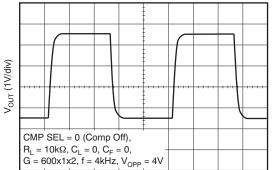

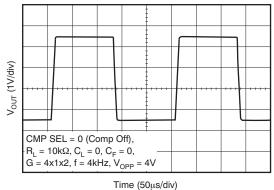

| V <sub>ouT</sub> /V <sub>IN</sub> Slew Rate<br>(Front End PGA + Output Amplifier)                               | CMP_SEL [CFG1 register] = 0                                                                                                                                                                           |      | 0.6                    |                          | V/µs          |  |

|                                                                                                                 | CMP_SEL [CFG1 register] = 1                                                                                                                                                                           |      | 0.3                    |                          | V/µs          |  |

| V <sub>OUT</sub> /V <sub>IN</sub> Settling Time (0.01%FSR)<br>(Front-End PGA + Output Amplifier)                | $\label{eq:V_OUT} V_{\text{IV}}  \text{differential gain = 8}, \\ V_{\text{OUT}} = +0.5V \; \text{to} \; +4.5V \; \text{step, comp off, no capacitve load}$                                           |      | 13                     |                          | μs            |  |

|                                                                                                                 | $\label{eq:V_OUT} V_{\text{IN}} \mbox{ differential gain = 200,} \\ V_{\text{OUT}} = +0.5 V \mbox{ to } +4.5 V \mbox{ step, comp off, no capacitve load}$                                             |      | 15                     |                          | μs            |  |

| External Sensor Output Sensitivity (2)                                                                          | $V_{S} = V_{REF} = V_{CLAMP} = +5V$                                                                                                                                                                   | 0.08 |                        | 296                      | mV/V          |  |

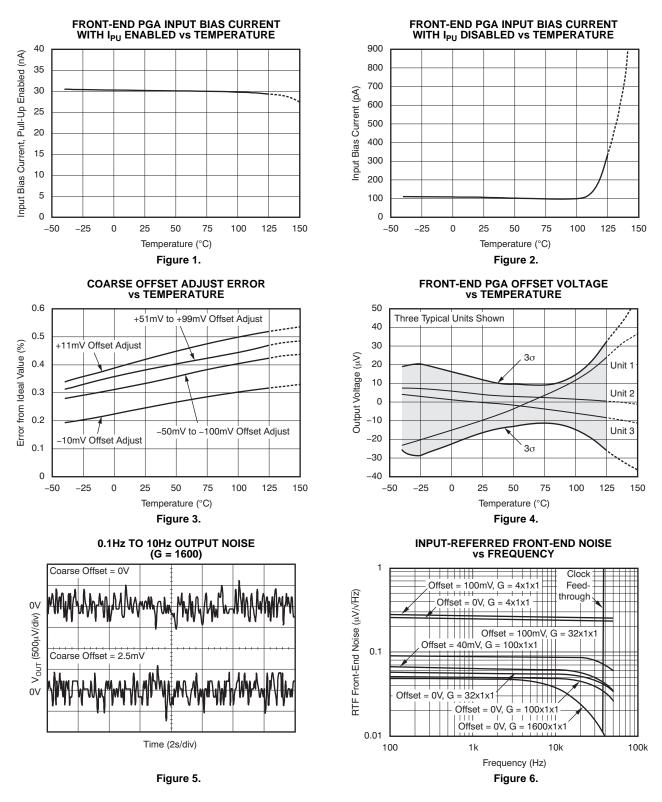

| FRONT-END PGA                                                                                                   |                                                                                                                                                                                                       |      |                        |                          |               |  |

| Auto-Zero Internal Frequency                                                                                    |                                                                                                                                                                                                       |      | 40                     |                          | kHz           |  |

| Offset Voltage (RTI) <sup>(3)</sup>                                                                             | Coarse Offset Adjust disabled                                                                                                                                                                         |      | ±5                     | ±40                      | μV            |  |

| vs Temperature                                                                                                  | Coarse Offset Adjust disabled                                                                                                                                                                         |      | ±0.2                   |                          | μ <b>ν/°C</b> |  |

| vs Supply Voltage, V <sub>S</sub>                                                                               | Coarse Offset Adjust disabled                                                                                                                                                                         |      | 2 + 150/G <sub>F</sub> | 10 + 1000/G <sub>F</sub> | μV/V          |  |

| vs Common-Mode Voltage                                                                                          | $G_F =$ Front-End PGA gain,<br>Coarse Offset Adjust disabled                                                                                                                                          |      | 1 + 250/G <sub>F</sub> | 10 + 2000/G <sub>F</sub> | μV/V          |  |

| Offset Voltage Programming Range (RTI) <sup>(3)</sup>                                                           | Coarse Offset Adjust enabled,<br>Coarse Offset Adjust controls offset                                                                                                                                 | -100 |                        | 100                      | mV            |  |

| vs Temperature                                                                                                  | Coarse Offset Adjust enabled                                                                                                                                                                          |      | ±0.2                   |                          | μ <b>ν/°C</b> |  |

| vs Supply Voltage, $V_S$                                                                                        | Coarse Offset Adjust enabled                                                                                                                                                                          |      | 2 + 150/G <sub>F</sub> |                          | μV/V          |  |

| vs Common-Mode Voltage                                                                                          | $G_F$ = Front End PGA gain,<br>Coarse Offset Adjust enabled                                                                                                                                           |      | 1 + 250/G <sub>F</sub> |                          | μV/V          |  |

| Linear Input Voltage Range <sup>(4)</sup>                                                                       |                                                                                                                                                                                                       | 0.2  |                        | V <sub>S</sub> - 1.4     | V             |  |

| Input Bias Current                                                                                              |                                                                                                                                                                                                       |      | ±0.3                   | ±1.5                     | nA            |  |

| vs Temperature                                                                                                  |                                                                                                                                                                                                       |      | 10                     |                          | pA/°C         |  |

| Input Offset Current                                                                                            |                                                                                                                                                                                                       |      | ±0.1                   | ±1.5                     | nA            |  |

| vs Temperature                                                                                                  |                                                                                                                                                                                                       |      | 10                     |                          | pA/°C         |  |

| Input Impedance: Differential                                                                                   |                                                                                                                                                                                                       |      | 30 🛛 6                 |                          | GΩ∥pF         |  |

| Input Impedance: Common Mode                                                                                    |                                                                                                                                                                                                       |      | 50 20                  |                          | GΩ∥pF         |  |

| Input Voltage Noise                                                                                             | RTI, dc to 10Hz, $G_F = 100$ , $R_S = 0\Omega$                                                                                                                                                        |      | 1.2                    |                          | $\mu V_{PP}$  |  |

| Input Voltage Noise Density                                                                                     | RTI, voltage noise density, f = 1kHz, Coarse Offset Adjust = $_{0V}$                                                                                                                                  |      | 50                     |                          | nV/√Hz        |  |

|                                                                                                                 | RTI, voltage noise density, f = 1kHz,<br>Coarse Offset Adjust = 100mV                                                                                                                                 |      | 80                     |                          | nV/√Hz        |  |

| Input EMI Filter Frequency<br>PGA Gain <sup>(5)</sup>                                                           | $\rm f_{3dB}$ Input EMI filter to GND, $\rm V_{IN1}$ and $\rm V_{IN2}$                                                                                                                                |      | 40                     |                          | MHz           |  |

| Gain Range Steps                                                                                                | 4, 6, 8, 12, 16, 32, 64, 100, 200, 400, 480, 600, 800, 960,<br>1200, 1600                                                                                                                             | 4    |                        | 1600                     | V/V           |  |

| Initial Gain Error                                                                                              | G <sub>F</sub> ≤ 16                                                                                                                                                                                   |      | ±0.03                  | ±0.25                    | %             |  |

|                                                                                                                 | $32 \le G_F \le 480$                                                                                                                                                                                  |      | ±0.1                   | ±0.4                     | %             |  |

|                                                                                                                 | $600 \le G_F \le 1600$                                                                                                                                                                                |      | ±0.3                   | ±1                       | %             |  |

| vs Temperature                                                                                                  |                                                                                                                                                                                                       |      | 6                      |                          | ppm/°C        |  |

| Output Voltage Range                                                                                            |                                                                                                                                                                                                       | 0.05 |                        | V <sub>S</sub> – 0.05    | V             |  |

| Bandwidth                                                                                                       | G <sub>F</sub> = 4                                                                                                                                                                                    |      | 400                    |                          | kHz           |  |

|                                                                                                                 | G <sub>F</sub> = 1600                                                                                                                                                                                 |      | 10                     |                          | kHz           |  |

(1) PGA308 total differential gain from input ( $V_{IN1} - V_{IN2}$ ) to output ( $V_{OUT}$ ):  $V_{OUT} / (V_{IN1} - V_{IN2}) =$  (PGA gain) x (output amplifier gain) x (fine gain adjust) with output amplifier internal gains used.

(2) Based on bridge sensor excitation voltage of +5V and PGA308 output voltage span of 4V. Individual applications must consider noise, small-signal bandwidth, and required system error to assess if the PGA308 will work for a given sensor sensitivity.

(3) RTI = Referred-to-input.

(4) Linear input range is the allowed min/max voltage on the V<sub>IN1</sub> and V<sub>IN2</sub> pins for the front-end PGA to continue to operate in a linear region. The allowed common-mode and differential voltage depends on gain and offset settings. Refer to the PGA308 User's Guide (SBOU069), for more information.

(5) I<sub>REF</sub> current load is typically 100µA while in Shutdown mode. Although the output amplifier is disabled in Shutdown mode, RFO and RGO (180kΩ typical total) remain connected in series between V<sub>FB</sub> and GND while in Shutdown mode. See Figure 37, *Detailed Block Diagram*, for more information.

#### SBOS440-JULY 2008

#### **ELECTRICAL CHARACTERISTICS (continued)**

**Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to +125°C. At  $T_A = +25^{\circ}C$ ,  $V_S = +5V$ , GND = 0V,  $D_{OUT}/V_{CLAMP} = +5V$ , and  $V_{REF} = +5V$ , unless otherwise noted.

| PARAMETER                                                     |                 | CONDITIONS                                                   | MIN                  | TYP   | MAX                   | UNIT          |

|---------------------------------------------------------------|-----------------|--------------------------------------------------------------|----------------------|-------|-----------------------|---------------|

| Coarse Offset Adjust<br>(RTI of Front-End PGA) <sup>(6)</sup> |                 |                                                              |                      |       |                       |               |

| Range                                                         |                 | $V_{REF} = +5V$                                              | -100                 |       | +100                  | mV            |

| Resolution                                                    |                 | 7 bit + sign, $V_{REF}$ = +5V                                |                      | 1     |                       | mV            |

| PSRR                                                          |                 |                                                              |                      | 2     |                       | μV/V          |

| CMRR                                                          |                 |                                                              |                      | 1     |                       | μV/V          |

| Drift                                                         |                 | Coarse Offset Adjust = 100mV                                 |                      | 1.2   |                       | μ <b>V/°C</b> |

| Fine Offset Adjust (Zero DAC)                                 |                 |                                                              |                      |       |                       |               |

| Programming Range                                             |                 | RTO of Front-End PGA                                         | -0.5V <sub>REF</sub> |       | +0.5V <sub>REF</sub>  | V             |

| Output Voltage Range                                          |                 |                                                              | 0.1                  |       | $V_{S} - 0.1$         | V             |

| Resolution                                                    |                 | 65,536 steps, 16-bit DAC, V <sub>REF</sub> = +5V             |                      | 76    |                       | μV            |

| Integral Nonlinearity                                         |                 |                                                              |                      | ±6    |                       | LSB           |

| Differential Nonlinearity                                     |                 |                                                              |                      | ±0.5  |                       | LSB           |

| Gain Error                                                    |                 |                                                              |                      | ±0.5  |                       | %             |

| Gain Error Drift                                              |                 |                                                              |                      | ±4    |                       | ppm/°C        |

| Offset                                                        |                 |                                                              |                      | ±4    |                       | mV            |

| Offset Drift                                                  |                 |                                                              |                      | ±10   |                       | μ <b>٧/°C</b> |

| PSRR                                                          |                 |                                                              |                      | ±200  |                       | μV/V          |

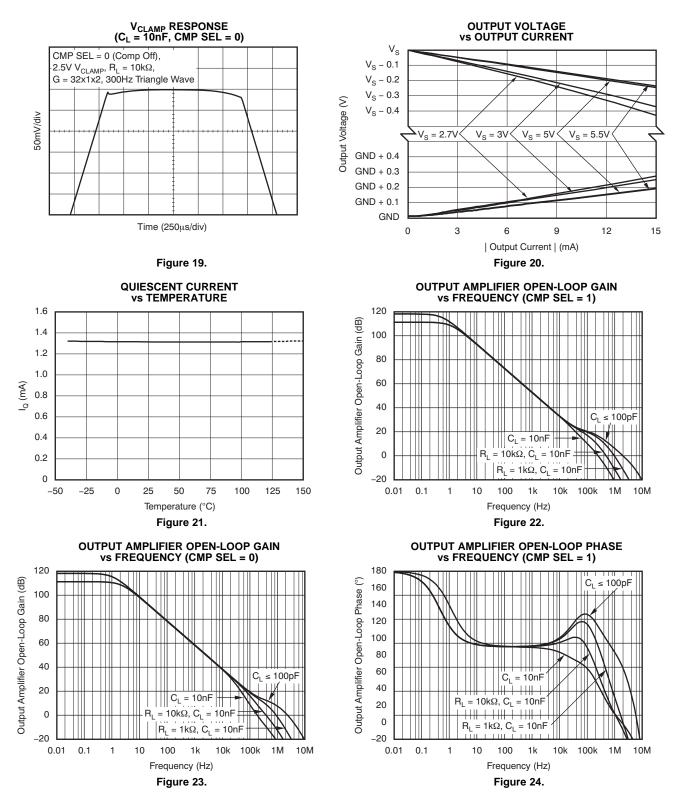

| Output Amplifier                                              |                 |                                                              |                      |       |                       |               |

| Output Fine Gain Adjust (Gain DAC)                            |                 |                                                              |                      |       |                       |               |

| Range                                                         |                 |                                                              | 0.33                 |       | 1                     | V/V           |

| Resolution                                                    |                 | 65,536 steps, 16-bit DAC                                     |                      | 10    |                       | μV/V          |

| Integral Nonlinearity                                         |                 |                                                              |                      | ±6    |                       | LSB           |

| Differential Nonlinearity                                     |                 |                                                              |                      | ±0.5  |                       | LSB           |

| Gain Error                                                    |                 |                                                              |                      |       | ±0.2                  | %             |

| Gain Drift                                                    |                 |                                                              |                      | 3     |                       | ppm/°C        |

| Output Amplifier                                              |                 |                                                              |                      |       |                       |               |

| Offset Voltage (RTI of Output Amplifier) <sup>(6)</sup>       |                 |                                                              |                      | ±3    |                       | mV            |

| vs Temperature                                                |                 |                                                              |                      | ±5    |                       | μ <b>ν/°C</b> |

| vs Supply Voltage, V <sub>S</sub>                             |                 |                                                              |                      | ±100  |                       | μV/V          |

| Common Mode Input Range                                       |                 |                                                              | 0                    |       | V <sub>s</sub> – 1.5  | V             |

| Input Bias Current                                            |                 |                                                              |                      | ±100  |                       | pА            |

| Amplifier Internal Gain                                       |                 |                                                              |                      |       |                       |               |

| Gain Range Steps                                              |                 | 2, 2.4, 3, 3.6, 4, 4.5, 6                                    | 2                    |       | 6                     | V/V           |

| Initial Gain Error                                            |                 |                                                              |                      | ±0.05 | ±0.25                 | %             |

| vs Temperature                                                |                 |                                                              |                      | ±1    |                       | ppm/°C        |

| Output Voltage Range                                          |                 | $I_{OUT} = 0.5 m A^{(7)}$                                    | 0.03                 |       | V <sub>S</sub> - 0.06 | v             |

|                                                               |                 | $I_{OUT} = 4mA^{(7)}$                                        | 0.1                  |       | V <sub>s</sub> – 0.1  | v             |

| Output Short Circuit Current                                  | I <sub>sc</sub> | Sourcing/sinking                                             | 10                   |       |                       | mA            |

| OpenLoop Gain at 0.1Hz                                        |                 |                                                              |                      | 106   |                       | dB            |

| Gain-Bandwidth Product                                        |                 |                                                              |                      | 2     |                       | MHz           |

| Phase Margin                                                  |                 | Gain = 2, $C_L$ = 200pF                                      |                      | 45    |                       | deg           |

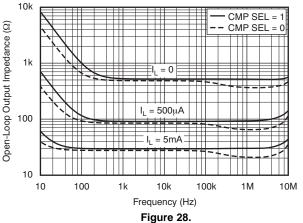

| Output Resistance                                             | Ro              | AC small signal, open loop, $f = 1MHz$ , $I_{OUT} = 0$ , see |                      | 500   |                       | Ω             |

|                                                               |                 | Figure 28                                                    |                      |       |                       |               |

(6) RTI = Referred-to-input.

4

(7) Unless limited by the over/under-scale setting, or V<sub>CLAMP</sub> Pin.

#### **ELECTRICAL CHARACTERISTICS (continued)**

**Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to +125°C. At  $T_A = +25^{\circ}C$ ,  $V_S = +5V$ , GND = 0V,  $D_{OUT}/V_{CLAMP} = +5V$ , and  $V_{REF} = +5V$ , unless otherwise noted.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                                                                                                                                                                 | PGA308                    | T                                              |                           |                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------|---------------------------|---------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | CONDITIONS                                                                                                                                                                      | MIN                       | ТҮР                                            | MAX                       | UNIT                      |

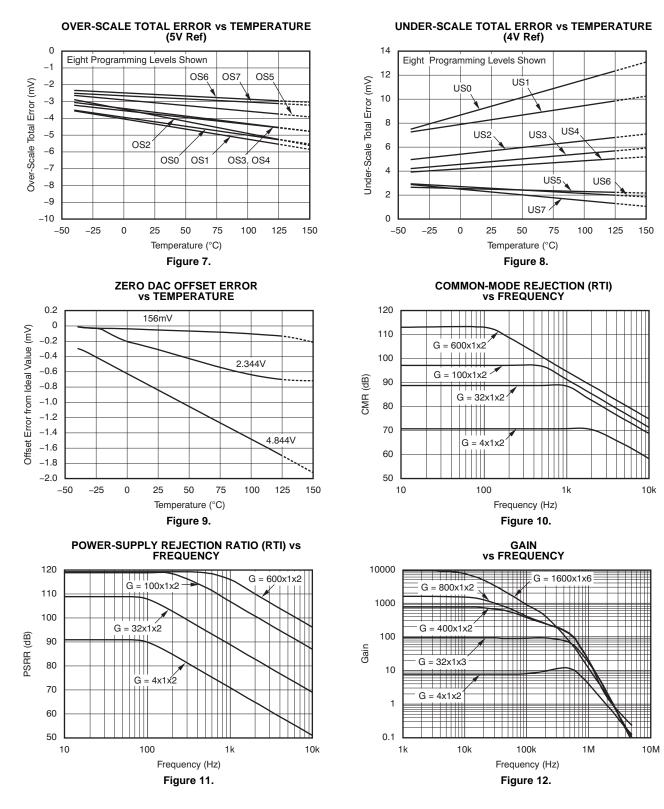

| Over- and Under-Scale Limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                                                                                                                                                                 |                           |                                                |                           |                           |

| Over-Scale Thresholds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | $V_{LIM}$ = 4V, register-selectable ratio of $V_{LIM}$                                                                                                                          |                           |                                                |                           |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OS0       | HL[2:0] (CFG1 register D[5:3]) = 000                                                                                                                                            | 0.97                      | 0.9805                                         | 0.99                      | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OS1       | HL[2:0] (CFG1 register D[5:3]) = 001                                                                                                                                            | 0.9588                    | 0.9688                                         | 0.9788                    | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OS2       | HL[2:0] (CFG1 register D[5:3]) = 010                                                                                                                                            | 0.9509                    | 0.9609                                         | 0.9709                    | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OS3       | HL[2:0] (CFG1 register D[5:3]) = 011                                                                                                                                            | 0.9392                    | 0.9492                                         | 0.9492                    | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OS4       | HL[2:0] (CFG1 register D[5:3]) = 100                                                                                                                                            | 0.8416                    | 0.8516                                         | 0.8616                    | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OS5       | HL[2:0] (CFG1 register D[5:3]) = 101                                                                                                                                            | 0.7673                    | 0.7773                                         | 0.7873                    | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OS6       | HL[2:0] (CFG1 register D[5:3]) = 110                                                                                                                                            | 0.6189                    | 0.6289                                         | 0.6389                    | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OS7       | HL[2:0] (CFG1 register D[5:3]) = 111                                                                                                                                            | 0.5603                    | 0.5703                                         | 0.5803                    | V/V                       |

| Over-Scale Threshold Tempco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                                                                                                                                                                 |                           | ±3                                             |                           | ppm/°0                    |

| Over-Scale Amplifier Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                                                                                                                                                                 |                           | ±9                                             |                           | mV                        |

| Over-Scale Amplifier Offset Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                                                                                                                                                                                 |                           | ±10                                            |                           | μ <b>V/°C</b>             |

| Under-Scale Thresholds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | $V_{LIM}$ = 5V, register-selectable ratio of $V_{LIM}$                                                                                                                          |                           |                                                |                           |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US7       | LL[2:0] (CFG1 register D[2:0]) = 111                                                                                                                                            | 0.0487                    | 0.0547                                         | 0.0607                    | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US6       | LL[2:0] (CFG1 register D[2:0]) = 110                                                                                                                                            | 0.04478                   | 0.05078                                        | 0.05678                   | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US5       | LL[2:0] (CFG1 register D[2:0]) = 101                                                                                                                                            | 0.04088                   | 0.04688                                        | 0.05288                   | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US4       | LL[2:0] (CFG1 register D[2:0]) = 100                                                                                                                                            | 0.03306                   | 0.03906                                        | 0.04506                   | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US3       | LL[2:0] (CFG1 register D[2:0]) = 011                                                                                                                                            | 0.02916                   | 0.03516                                        | 0.04116                   | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US2       | LL[2:0] (CFG1 register D[2:0]) = 010                                                                                                                                            | 0.02525                   | 0.03125                                        | 0.03725                   | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US1       | LL[2:0] (CFG1 register D[2:0]) = 001                                                                                                                                            | 0.01743                   | 0.02343                                        | 0.02943                   | V/V                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US0       | LL[2:0] (CFG1 register D[2:0]) = 000                                                                                                                                            | 0.01353                   | 0.01953                                        | 0.02553                   | V/V                       |

| Inder-Scale Threshold Tempco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                                                                                                                                                                 |                           | ±3                                             |                           | ppm/°                     |

| Jnder-Scale Amplifier Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                                                                                                                                                                 |                           | ±9                                             |                           | mV                        |

| Under-Scale Amplifier Offset Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                                                                                                                                                                 |                           | ±10                                            |                           | μ <b>ν/°C</b>             |

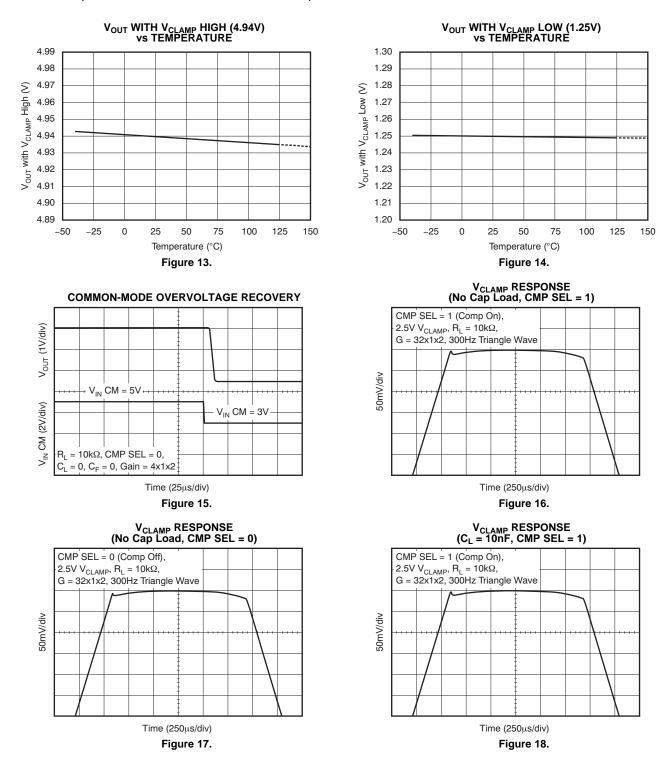

| Output Voltage Clamp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                                                                                                                                                                                 |                           |                                                |                           |                           |

| nput Voltage Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | $V_{CLAMP} \le V_S, V_S = +5V$                                                                                                                                                  | 1.25                      |                                                | 4.95                      | V                         |

| nput Bias Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                                                                                                                                                                                 |                           | ±60                                            |                           | nA                        |

| V <sub>OUT</sub> Clamp Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                                                                                                                                                                 | V <sub>CLAMP</sub> - 0.05 | V <sub>CLAMP</sub>                             | V <sub>CLAMP</sub> + 0.05 | V                         |

| Fault Monitor Circuit<br>External Comparators)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                                                                                                                                                                 |                           |                                                |                           |                           |

| INP_HI Comparator Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | Fault Detect Mode Select = 0 (bridge fault); see CFG1                                                                                                                           | Smaller                   | • of (V <sub>s</sub> – 1.2) or (0              | 65\/)                     | v                         |

| INN_HI Comparator Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | register                                                                                                                                                                        | Ontailei                  | 01 (Vg = 1.2) 01 (0                            | .00 VFLT)                 | v                         |

| NP_LO Comparator Threshold<br>NN_LO Comparator Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | Fault Detect Mode Select = 0 (bridge fault); see CFG1 register                                                                                                                  | Large                     | er of (0.1V) or (0.38                          | 5V <sub>FLT</sub> )       | V                         |

| Fault Monitor Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $V_{FLT}$ | Fault Monitor Reference; see CFG1 register, FLT REF bit sets $V_{\text{FLT}}$                                                                                                   |                           | $\rm V_S$ or $\rm V_{REF}$                     |                           | V                         |

| NP_HI Comparator Threshold<br>NN_HI Comparator Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | Fault Detect Mode Select = 1 (common mode fault); see<br>CFG1 register                                                                                                          |                           | V <sub>S</sub> – 1.2                           |                           | V                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                                                                                                                                                                 |                           |                                                |                           |                           |

| NP_LO Comparator Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | Fault Detect Mode Select = 1 (common mode fault); see<br>CFG1 register                                                                                                          | 70                        | 100                                            | 130                       | mV                        |

| NP_LO Comparator Threshold<br>NN_LO Comparator Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                                                                                                                                                                 | 70                        | 100<br>7                                       | 130                       | mV<br>mV                  |

| NP_LO Comparator Threshold<br>NN_LO Comparator Threshold<br>Comparator Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                                                                                                                                                                                 | 70                        |                                                | 130                       |                           |

| NP_LO Comparator Threshold<br>NN_LO Comparator Threshold<br>Comparator Hysteresis<br>Comparator Input Offset Voltage<br>Fault Monitor Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                                                                                                                                                                                 | 70                        | 7                                              | 130                       | mV                        |

| NP_LO Comparator Threshold<br>NN_LO Comparator Threshold<br>Comparator Hysteresis<br>Comparator Input Offset Voltage<br>Fault Monitor Circuit<br>Internal Comparators)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                                                                                                                                                                 | 70                        | 7                                              | 130                       | mV                        |